18. シュミットトリガ、3ステート

シュミットトリガ(Schmitt Trigger)は、ディジタル回路やアナログ回路において使用される特殊な増幅器である。シュミットトリガは、入力信号のノイズや不安定性に対して強く、入力信号がある閾値を超えた時に出力を切り替える特性(ヒステリシス特性:履歴特性)を持っている。このヒステリシス特性によって信号の不安定性を抑制できる。

3ステート(Three-State)は、ディジタル回路の出力の状態の一つである。通常、ディジタル回路の出力は「High」(高い電圧)、または「Low」(低い電圧)のいずれかの状態になるが、3ステートではさらに1つの状態が加わり、出力は「High」、 「Low」、「High-Impedance」の3つの状態を持つ。

シュミットトリガ

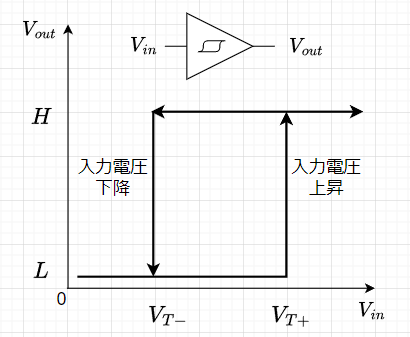

図1上図のように普通のディジタル入力では、信号が変動する場合、閾値周辺でのノイズによって出力は図のようにHとLがバタバタと変化してしまう。それに対して、シュミットトリガでは、図1下図のように\(V_{T+}\)を越えるまで、出力はHレベルに変化しない。また、出力がLレベルに変化するためには、入力は、\(V_{T-}\)以下になる必要がある。このようにシュミットトリガ入力により、ノイズの影響を受け難くなる。図2にシュミットトリガ入力のバッファの入出力特性を示す。

コンパレータによるシュミットトリガ

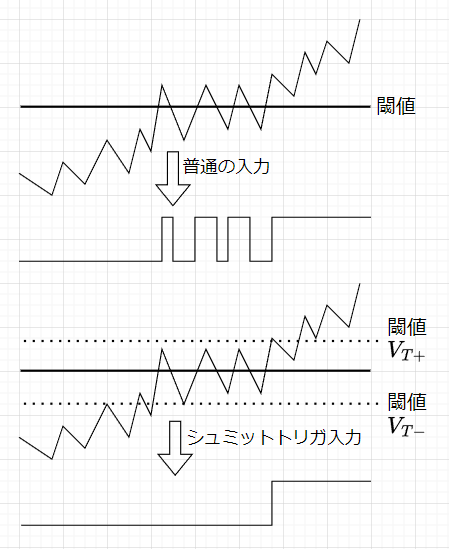

シュミットトリガの実装の一つとして、オペアンプによるコンパレータ(比較器)を利用したものがある。図3がその回路図である。コンパレータは非反転入力と反転入力の電位差を増幅して飽和させたものを出力する。非反転入力が反転入力よりも高い電圧にあるとき\(+V_{CC}\)を出力し、非反転入力が反転入力以下の電圧であるときには\(-V_{CC}\)を出力する。この出力を抵抗\(R2\)で非反転入力に帰還する。出力が\(+V_{CC}\)のときには、非反転入力には\(+V_{CC}\)と入力電圧\(V_{in}\)の差を\(R2\)と\(R1\)で分圧した電圧が入力される。この電圧が反転入力である\(0\;V\)を下回るまでの間は出力は\(+V_{CC}\)のままである。この閾値となる電圧は、$$\frac{V_{in}}{R1} = -\frac{V_{CC}}{R2}$$よって、$$V_{in}=-\frac{R1}{R2} V_{CC}$$である。

シュミットトリガ

(LTspice)

シュミットトリガ

シミュレーション結果

\(V_{in}\)が一度この電圧を下回れば出力が\(-V_{CC}\)になるため、今度は非反転入力には\(-V_{CC}\)と入力電圧\(V_{in}\)の差を\(R2\)と\(R1\)で分圧した電圧が入力されることとなる。このとき非反転入力が反転入力の\(0\;V\)より大きくなる条件は、$$\frac{V_{in}}{R1} = \frac{V_{CC}}{R2}$$よって、$$V_{in}=\frac{R1}{R2} V_{CC}$$となる。

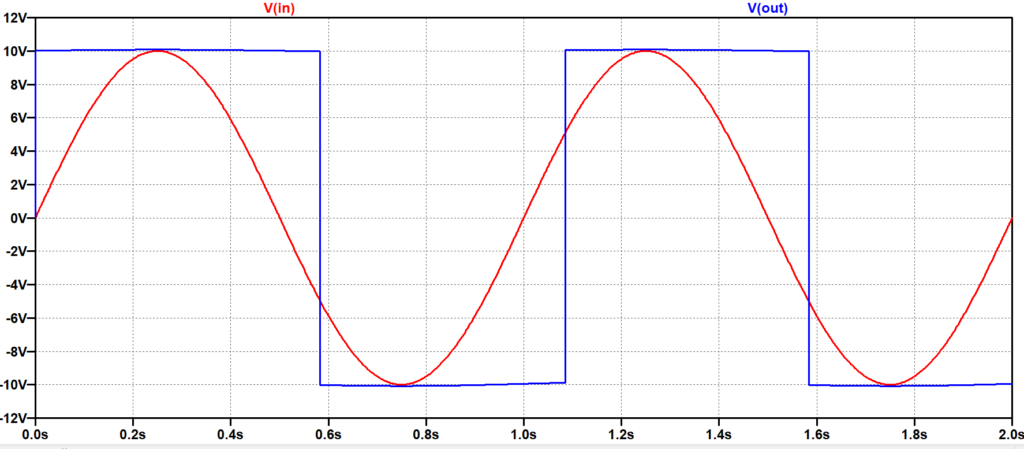

図4は、図3の回路のシミュレーション結果である。入力\(V_{in}\)(赤線)は振幅\(10\;V\)の正弦波である。閾値は\(\pm \frac{R1}{R2} V_{CC} =\pm 5\; V\)なので、青線のように変化し、ヒステリシス特性となっていることが分かる。

ディジタル回路のシュミットトリガ

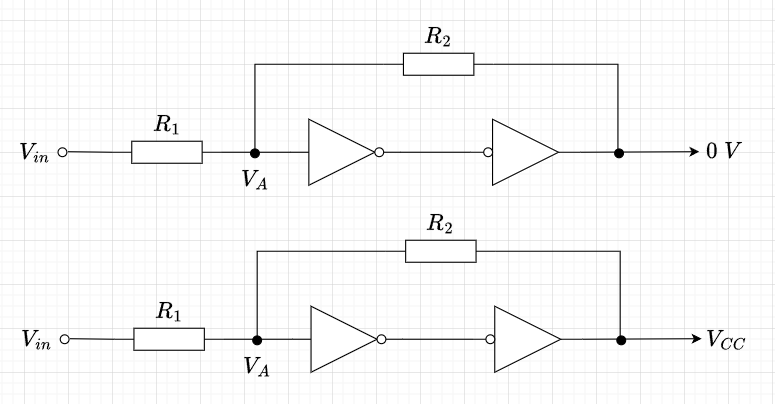

シュミットトリガ特性は、図5に示すように出力のフィードバックによって実現できる。図5上図のように出力が\(0\;V\)の状態から\(L \rightarrow H\)に変化する場合、\(A\)点の電圧は、$$V_A = \frac{R_2}{R_1 + R_2}V_{in}$$となる。

論理ゲートをCMOSの回路とすると、閾値はほぼ電源電圧\(V_{CC}\)の半分なので、点\(A\)が閾値を超すには、$$V_A = \frac{R_2}{R_1 + R_2}V_{in} > \frac{V_{CC}}{2}$$なので、\(V_{in}\)が達する必要がある電圧\(V_{T+}\)は、$$V_{T+}= \frac{R_1+R_2}{R_2} \frac{V_{CC}}{2}$$となる。

図5下図のように出力が\(V_{CC}\)の状態から\(H \rightarrow L\)に変化する場合、\(A\)点の電圧は、$$V_A = \frac{R_1}{R_1 + R_2}(V_{CC} - V_{in}) + V_{in}$$となる。点\(A\)が閾値を超すには、$$V_A = \frac{R_1}{R_1 + R_2}(V_{CC} - V_{in}) + V_{in} < \frac{V_{CC}}{2}$$なので、\(V_{in}\)が達する必要がある電圧\(V_{T-}\)は、$$V_{T-} = \frac{R_2 - R_1}{R_2} \frac{V_{CC}}{2}= V_{CC} - V_{T+}$$となる。このようにして、\(V_{T+}\)、\(V_{T-}\)が決まり、ヒステリシス特性をディジタル回路で実現できる。なお、シュミットトリガ特性を持つ論理IC 7414において、閾値の幅(\(V_{T+}\)と\(V_{T-}\)の差)は、約\(0.8 \;V\)程度であり、十分なノイズ耐性を持っている。

CMOSの論理素子

CMOSのNOT回路、バッファ回路、シュミットトリガ回路を構成する方法の詳細は以下を参考にして下さい。

・CMOSで作るシュミット・トリガ回路

3ステート出力

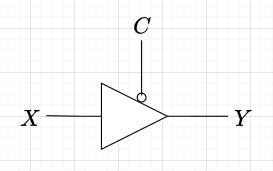

3ステートバッファの例を図6に、その動作表を表1に示す。この論理素子は、アクティブローの制御端子\(C\)を持つ。この端子がLのときは、通常のバッファとして動作する。しかし、\(C\)がHになると出力が電気的に切り離された状態(フローティング状態)になり、この状態をハイインピーダンス状態(Hi-Z)という。このため、この論理素子の出力が、H、L、Hi-Zの3つの状態を持つことから、3ステートまたはトライステート出力と呼ばれる。

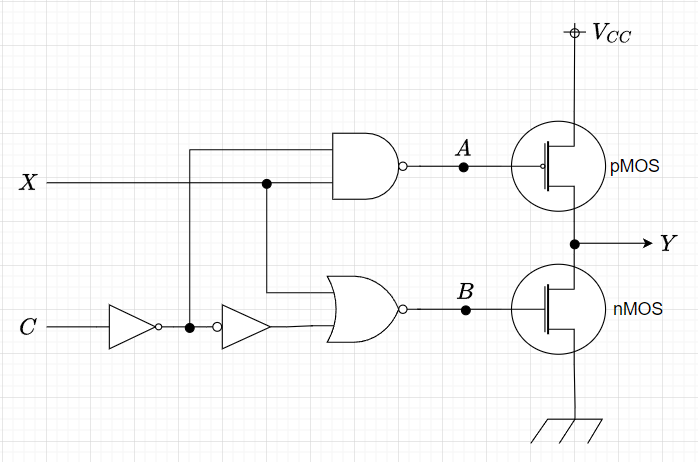

図7はCMOSによる3ステート回路の例である。表2に示す動作表のように、制御端子\(C\)がHになると、出力回路のpMOS、nMOSともOFFとなるため、出力\(Y\)は電気的に切り離されたフローティング状態、Hi-Zとなる。

3ステートの論理素子は、バスを構成する場合などに標準的に使用される。

バス

バスは、コンピュータ等の内部または外部で、複数のデバイス間でデータを伝送するための共有伝送路のことである。バスを使用することで、複数のデバイス間で効率的にデータをやり取りすることができる。バスの例は以下である。

・アドレスバス:メモリやI/Oデバイスなどのアドレスを伝送するために使用される。アドレスバスの幅は、アクセス可能なメモリやデバイスの基本的な最大容量を決める。

・データバス:データを伝送するために使用される。データバスの幅は、一度に伝送できるデータ量を決める。

| \(C\) | \(X\) | \(Y\) |

| L | L | L |

| L | H | H |

| H | L | Hi-Z (ハイインピーダンス) |

| H | H | Hi-Z |

| \(C\) | \(X\) | \(A\) | \(B\) | pMOS | nMOS | \(Y\) |

| L | L | H | H | OFF | ON | L |

| L | H | L | L | ON | OFF | H |

| H | L | H | L | OFF | OFF | Hi-Z |

| H | H | H | L | OFF | OFF | Hi-Z |

動作表