8. DTLとTTL

ダイオードによる論理回路は、実用的ではない。これは、ダイオードがスイッチング動作をするものの、受動素子であるため負荷を駆動する能力が無いためである。この問題を解消するために能動素子であるトランジスタと組み合わせることが考えられる。その一種であるDTL(Diode-Transistor Logic)は、バイポーラトランジスタ、ダイオード、抵抗で構成される。DTL論理回路は、シンプルで低コストで実現できるというメリットがあるが、高速動作や低消費電力が求められる用途には、より高性能なTTL論理回路が用いられる。TTL(Transistor-Transistor Logic)は、トランジスタとトランジスタを用いた論理回路の方式で、DTLに代わって広く用いられている。

DTLの構成と動作

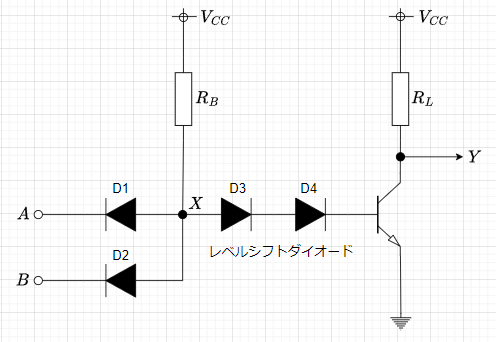

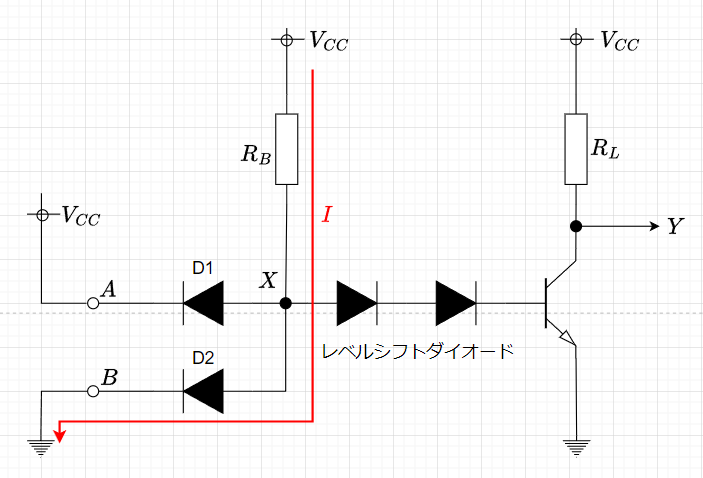

図1にDTLの基本回路を示す。\(A,B\)端が入力、\(Y\)が出力とする。

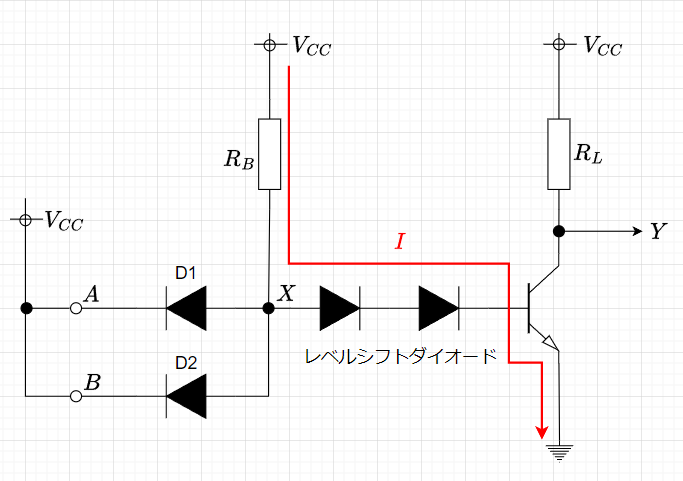

図2のように、\(A,B\)ともにHレベル(\(V_{CC}\))とすると、ダイオード\(D1,D2\)ともにOFFとなる。この時、レベルシフトダイオード、トランジスタのベース-エミッタ間とも順方向バイアスとなるため、トランジスタはON状態となり、電流\(I\)は図の赤線のように流れる。従って、\(X\)点の電圧は、約\(1.8 \;V\)で、出力\(Y\)(\(V_{CE(sat)}\):コレクタエミッタ間飽和電圧)は、約\(0 \; V\)(実際は、\(0.1 \; V\)程度)となる。図3のように、\(B\)をLレベル(\(0 \; V\))とすると、ダイオード\(D2\)がONとなる。従って、\(X\)点の電圧は、\(0.6 \; V\)となり、レベルシフトダイオードがあるため、トランジスタの\(V_{BE}\)は\(0.6 \; V\)以上になることはないので、トランジスタはOFFとなる。その結果、出力\(Y\)の電圧は、\(V_{CC}\)となる。以上の結果をふまえ、このDTLの動作を表1にまとめる。表1より、図1のDTL回路がNAND回路となっていることがわかる。

NAND演算の完全性より、全ての論理回路がDTLで構成できると言える。

| \(A\) | \(B\) | \(Y\) | |||

| \(0 \; V\) | 0 | \(0 \; V\) | 0 | \(V_{CC}\) | 1 |

| \(0 \; V\) | 0 | \(V_{CC}\) | 1 | \(V_{CC}\) | 1 |

| \(V_{CC}\) | 1 | \(0 \; V\) | 0 | \(V_{CC}\) | 1 |

| \(V_{CC}\) | 1 | \(V_{CC}\) | 1 | \(0 \;V\) | 0 |

TTLの構成と動作

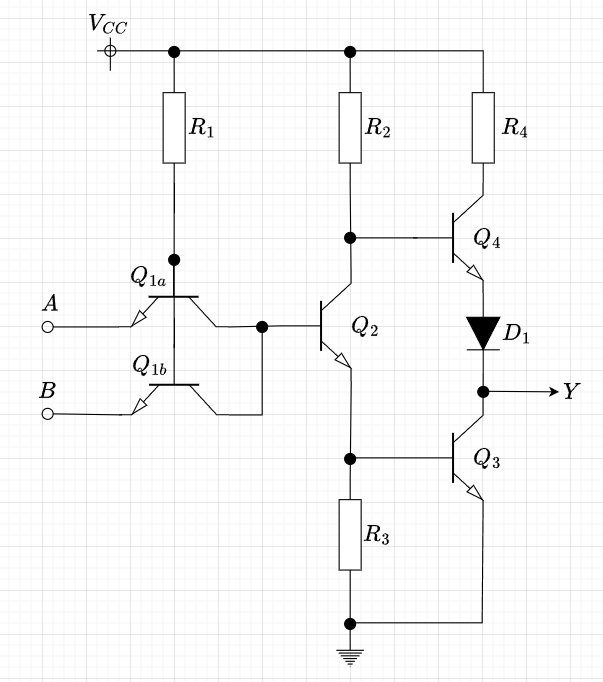

図4にTTLの基本回路を示す。バイポーラトランジスタ\(Q_{1a}, \;Q_{1b}\)はnpn接合で構成されているので、B(ベース)-E(エミッタ)間が図1のD1、D2に相当し、B(ベース)-C(コレクタ)間がD3に相当する。なお、\(Q_{1a}, \;Q_{1b}\)は、普通のトランジスタとは異なり、ベース、コレクタが共通で、エミッタが2個あるマルチエミッタトランジスタである。

(バイポーラトランジスタの動作に関しては、トランジスタの動作原理を参照して欲しい。)

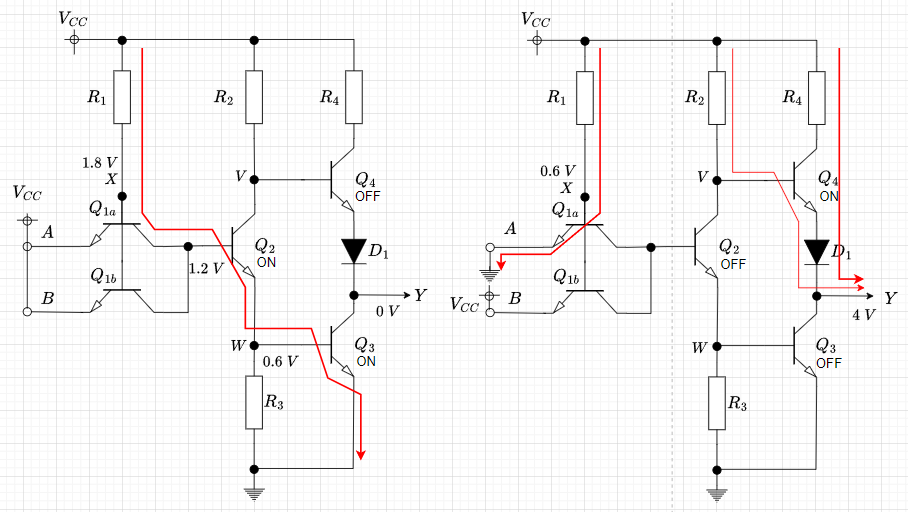

図5が基本動作である。左図は、\(A,B\)端子ともHレベル(\(V_{CC}\))にした場合で、トランジスタ\(Q_2\)、\(Q_3\)がONとなる。\(Q_4\)はOFFとなり、その結果、出力\(Y\)は\(0\;V\)となる。

右図は、\(A\)端子をLレベル(\(0\;V\))、\(B\)端子をHレベル(\(V_{CC}\))にした場合で、トランジスタ\(Q_2\)、\(Q_3\)がOFFとなる。\(Q_4\)はONとなり、その結果、出力\(Y\)は約\(4\;V\)となる。

以上の動作は、基本的にDTLのNAND回路と同様である。

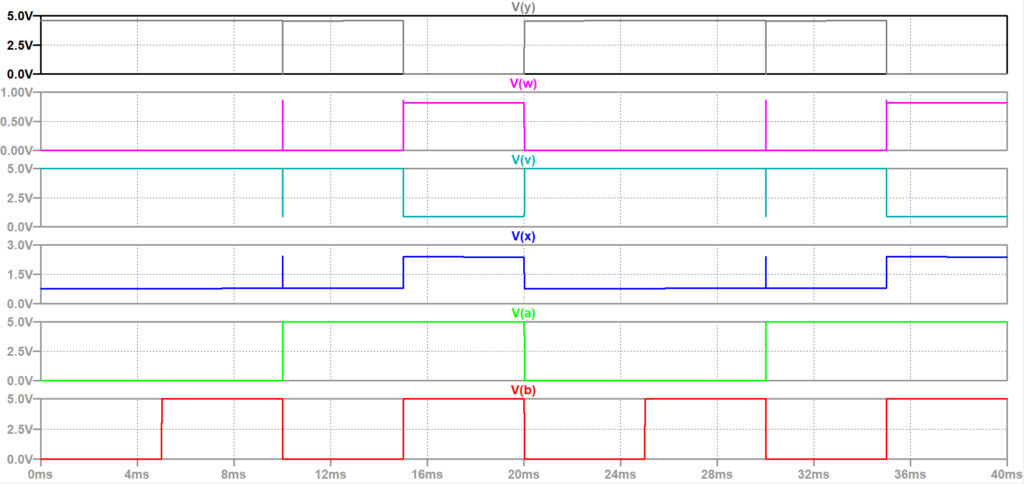

TTLの動作シミュレーション(LTspice)

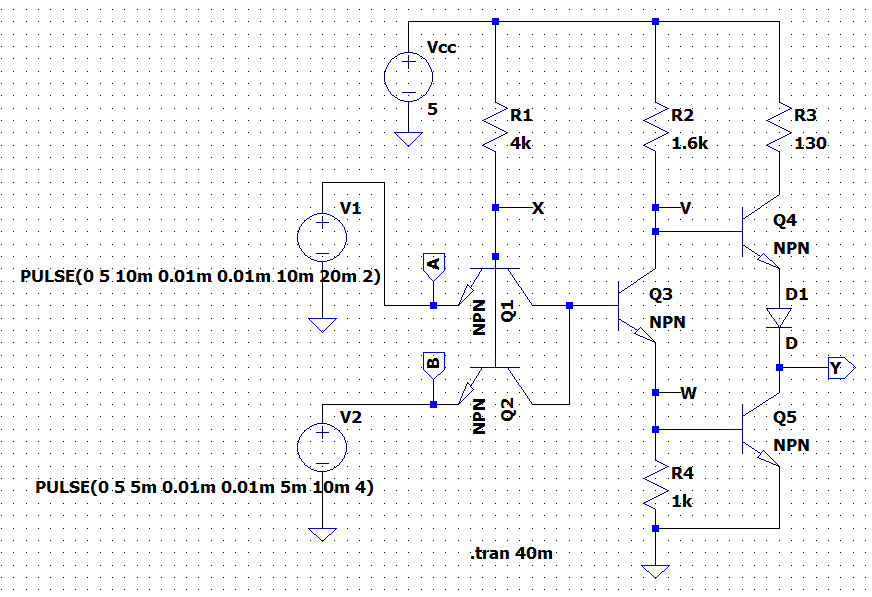

図6はTTLの動作をシミュレーションするためのLTspice回路図である。端子\(A\)にL,L,H,H,L,L,H,H(V(a))、端子\(B\)にL,H,L,H,L,H,L,H(V(b))の方形波を与えている。このとき、X,V,W点の電圧をV(x),V(v),V(w)に示す。また、出力電圧はV(y)となる。表2に動作をまとめる。

| V(a) | V(b) | V(x) | V(v) | V(w) | V(y) | |||

| \(0\;V\) | 0 | \(0\;V\) | 0 | \(0.8 \;V\) | \(5\;V\) | \(0\;V\) | \(4.6 \;V\) | 1 |

| \(0\;V\) | 0 | \(5\;V\) | 1 | \(0.8 \;V\) | \(5\;V\) | \(0\;V\) | \(4.6 \;V\) | 1 |

| \(5\;V\) | 1 | \(0\;V\) | 0 | \(0.8 \;V\) | \(5\;V\) | \(0\;V\) | \(4.6 \;V\) | 1 |

| \(5\;V\) | 1 | \(5\;V\) | 1 | \(2.4 \;V\) | \(0.9 \;V\) | \(0.8 \;V\) | \(0\;V\) | 0 |