15. 差動増幅回路

差動増幅回路とは、2つの入力信号の差分を増幅する回路である。従って、2つの入力信号が同じ値(周波数、振幅、位相が同じ)であれば、出力はゼロになる。差動増幅回路は、入力信号の同相成分(例えば、同相の共通雑音)を除去するのに有効で、雑音を抑圧して信号のみを増幅することができる。

差動増幅回路の主要な特性として、・入力信号の同相成分を除去できる、・利得が高い、・インピーダンスが高い、が挙げられる。

差動増幅回路は、さまざまな電子回路で用いられる。具体的な用途としては、オペアンプ、アンプ、コンパレータ、変調回路、受信機などがある。

※以下、BJTはバイポーラトランジスタの略である。

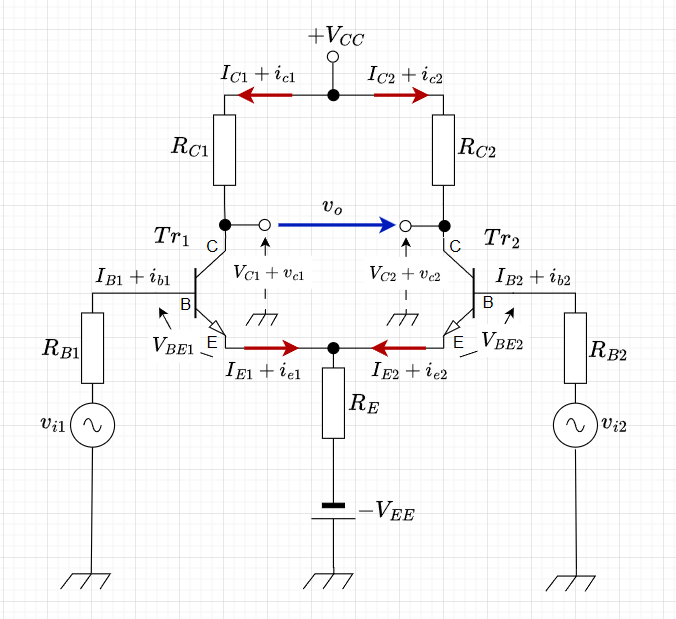

図1は、「差動増幅回路の基本回路図」である。2個のBJT\(Tr_1,\;Tr_2\)の特性は等しく、\(R_{C1}=R_{C2}\)、\(R_{B1} = R_{B2}\)として、左右対称の回路を構成する。電源は\(+V_{CC}\)と\(-V_{EE}\)の2電源で、図の回路構成より、\(Tr_1,\;Tr_2\)のエミッタ電圧は、ベース電圧より低く、これがバイアス電圧\(V_{BE}\)となる。2組の入力端子\(v_{i1},\;v_{i2}\)より供給される電圧の差を増幅して、両BJTのコレクタから出力を取り出す。出力が二つの入力電圧の差に比例するため、差動増幅回路という。

ここで、\(v_{i1}=v_{i2}=0\)とすると、$$I_{B1}=\frac{V_{EE}-R_E(I_{E1} + I_{E2})-V_{BE1}}{R_{B1}} \\ I_{B2}=\frac{V_{EE}-R_E(I_{E1} + I_{E2})-V_{BE2}}{R_{B2}} $$となる。\(Tr_1,\;Tr_2\)の特性は等しいので、\(V_{BE1} = V_{BE2}\)と見なせ、その結果、\(I_{B1}=I_{B2}\)となり、\(I_{C1} =\beta I_{B1} = \beta I_{B2} = I_{C2}\) となる。このとき、$$V_{C1} = V_{CC} - R_{C1} I_{C1} \\V_{C2} = V_{CC} - R_{C2}I_{C2}$$であるが、\(R_{C1}=R_{C2}\)、\(I_{C1}=I_{C2}\)より、\(V_{C1} = V_{C2}\)となる。その結果、出力\(v_o= V_{C2} - V_{C1} = 0\)となる。つまり、差動増幅回路では、電源電圧や温度の変化によってBJTの動作点が変動しても、出力には現れないドリフトの低減作用がある。(※ドリフト:入力信号を加えなくても、回路内で生じた変動が増幅されて出力に現れることをいう。)

差動増幅回路の動作(LTspice)

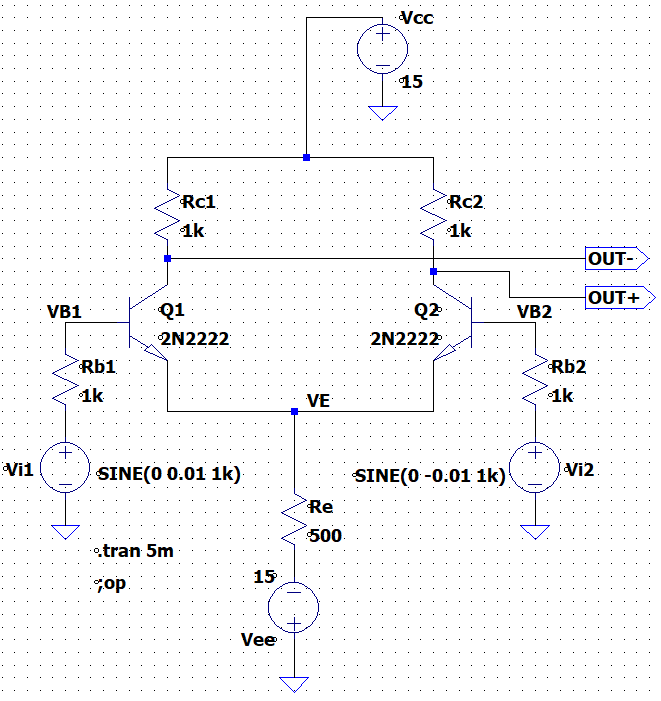

図2「差動増幅回路(LTspice)」は、LTspiceによる解析用の回路図である。入力端子は2箇所で、vi1, vi2 の信号を入力する。出力はQ1、Q2のコレクタ電圧でOUT+とOUT-から取り出す。

(1)片側の入力端子のみに信号を印可した場合

vi1のみに信号(正弦波:振幅 0.01 V(10 mV)、周波数 1 kHz)を加え、図3の信号設定のようにvi2 = 0 Vとする。

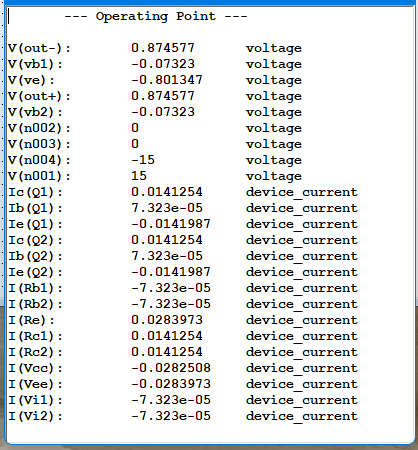

図4は、動作点(DC解析)の解析結果である。この結果から、例えば、BJT Q1の\(V_{BE}\)は、\(V_{BE} \)= vb1 - ve \(\approx 0.73 \; V \) となっていることがわかる。

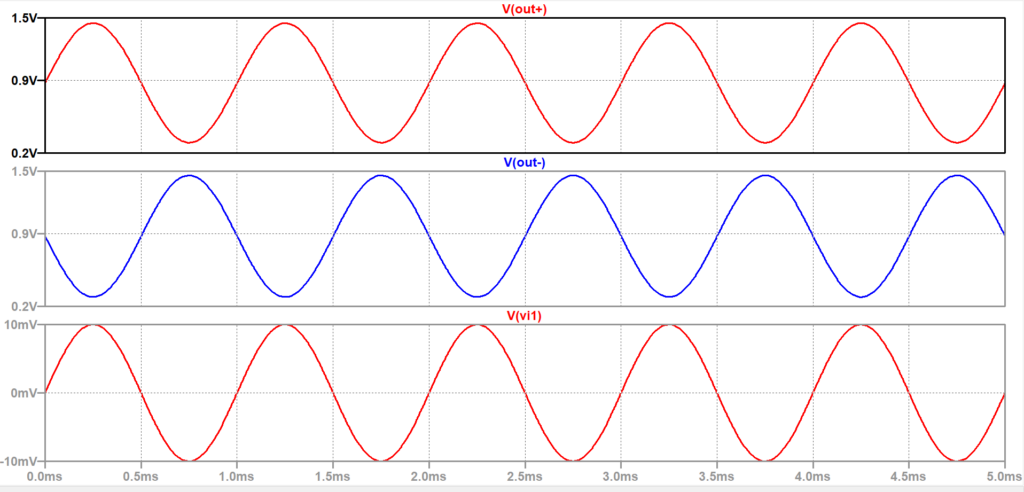

図5は、片側の入力端子のみに信号を印可した場合のシミュレーション結果である。vi1(下段)は、振幅10 mV、周期1 msの正弦波で、OUT- は入力信号に対して位相は逆相で、振幅0.58 V、OUT+ は入力信号に対して位相は同相で、振幅0.58 Vである。従って、増幅度は58倍(約35 dB)である。出力信号をOUT+とOUT-の差とした場合、振幅は約1.2 Vで、増幅度は120倍(約42 dB)となる。

vi1:下段、out-:中段、out+:上段

(2) 両側の入力端子に同一(同相)の信号を印可した場合

vi1の信号(正弦波:振幅 0.01 V(10 mV)、周波数 1 kHz)とvi2を同一にし、図6の信号設定のようにvi2の信号を(正弦波:振幅 0.01 V(10 mV)、周波数 1 kHz)とする。vi1とvi2は同相である。

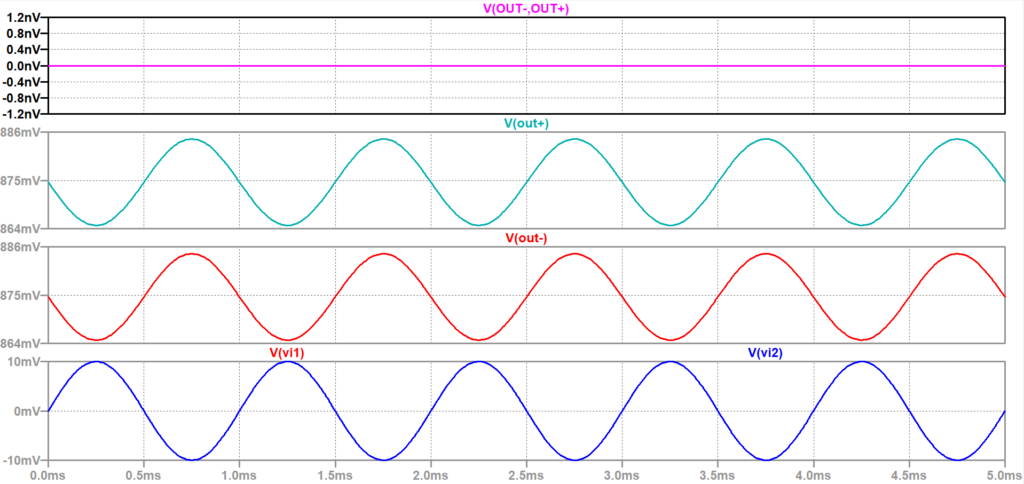

図7は、両側の入力端に同一の信号を印可した場合のシミュレーション結果である。vi1、vi2(下段)は、振幅10 mV、周期1 msの同相の正弦波である。このとき、OUT- 、OUT+とも入力信号に対して逆相となり、OUT-、OUT+ は同相で、同じ振幅となる。その結果、出力信号\(v_o\)をOUT+とOUT-の差とした場合、出力は、ほぼ0となる。これは入力信号の同相成分(例えば、同相の共通雑音)を除去できることを示唆している。

vi1=vi2:下段、out-,out+:中段、\(v_o\):上段

(3)両側の入力端子に逆相の信号を印可した場合

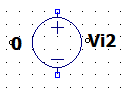

vi1の信号(正弦波:振幅 0.01 V(10 mV)、周波数 1 kHz)とvi2の信号を逆相にする。図8の信号設定のようにvi2の信号を(正弦波:振幅 0.01 V(10 mV)、周波数 1 kHz)とする。vi1とvi2は逆相である。

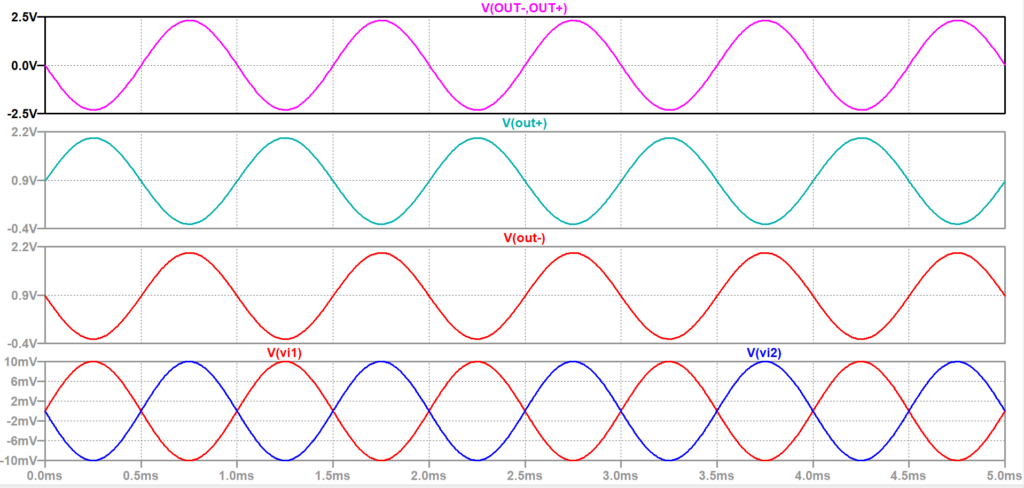

図9は、両側の入力端に逆相の信号を印可した場合のシミュレーション結果である。vi1(下段)は、振幅10 mV、周期1 msの正弦波で、vi2は逆相の信号である。OUT-とOUT+ は逆相で、同じ振幅となる。その結果、出力信号\(v_o\)をOUT+とOUT-の差とした場合、出力は倍となる。このシミュレーションの場合、入力信号振幅10 mVに対して、出力信号\(v_o\)の振幅は約2.4 Vとなる。従って、増幅度は240倍(約48 dB)である。

vi1,vi2:下段、out-,out+:中段、\(v_o\):上段