15. フリップフロップ

フリップフロップは、1ビットの情報を保持する(記憶する)ことができる論理回路である。フリップフロップは、ディジタルメモリ、タイミング制御回路、シーケンシャル回路などに広く利用されている。フリップフロップの基本的な構成は、論理ゲート、トランジスタ、抵抗などで構成された回路である。フリップフロップには、さまざまな種類があるが、RSフリップフロップ、Dフリップフロップ、JKフリップフロップなどがある。

RSフリップフロップ

RSラッチ

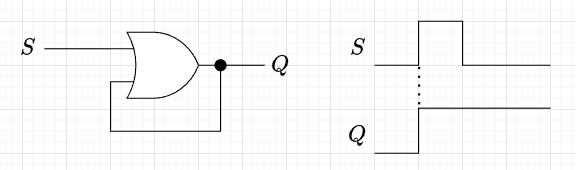

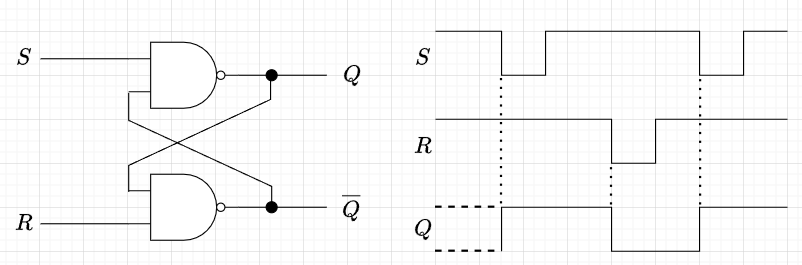

図1がラッチの基本である。図1(右)のタイミングチャートのように入力\(S\)(セット)が一旦Hになると出力\(Q\)がHとなり、\(S\)の変化に関わらずHが維持される。これは\(S\)の最初の変化の状態が記憶されたことになる。しかしながら、この回路では、\(S\)にLが入力されてもそれが記憶されることがないので、実用的とは言えない。

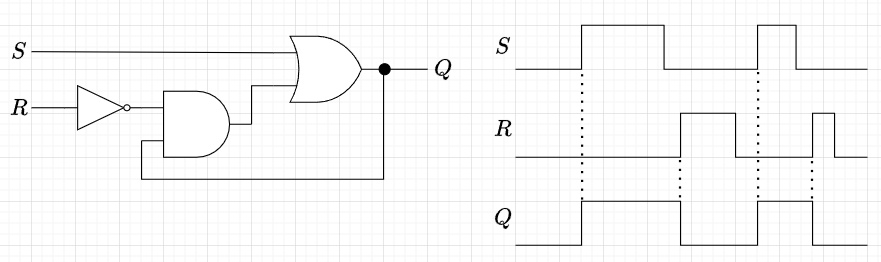

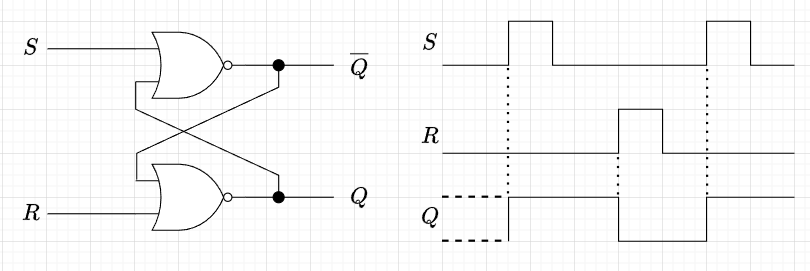

図2は、\(R\)(リセット)ゲートを付け加えることで、HでもLでも記憶できるようにしたRSラッチである。また、図2の回路を変換することで、図3のNOR形RSラッチが得られる。NOR形RSラッチのタイミングチャートを図3(右)に示す。また、図4のようにNAND素子を使ったNAND形RSラッチもある。この場合は、負論理入力で動作する。NAND形RSラッチのタイミングチャートを図4(右)に示す。

正論理、負論理

正論理(positive logic)と負論理(negative logic)は、ディジタル回路において信号の表現方法や論理値の扱いに関連する概念である。

*正論理では、一般的に次のようなルールが適用される。

・論理1(真)は高い電圧を表し、論理0(偽)は低い電圧を表す。

・肯定的な(true)条件は高い電圧または論理1に対応し、否定的な(false)条件は低い電圧または論理0に対応する。

*負論理では、正論理とは逆に次のようなルールが適用される。

・論理1(真)は低い電圧を表し、論理0(偽)は高い電圧を表す。

・肯定的な(true)条件は低い電圧または論理1に対応し、否定的な(false)条件は高い電圧または論理0に対応する。

同期式RSフリップフロップ

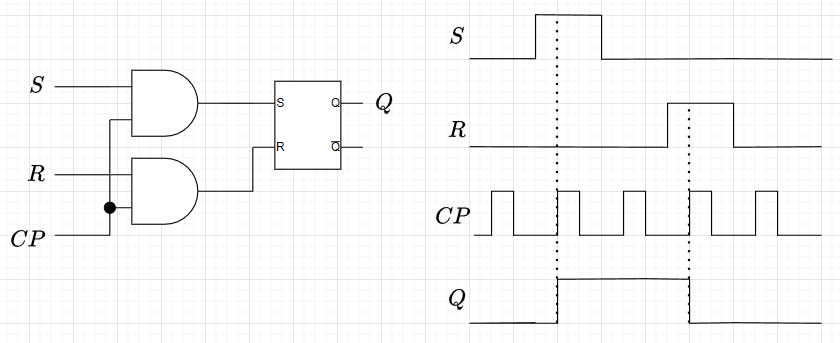

同期式RSフリップフロップは、クロック信号によって制御され、クロックの立ち上がりまたは立ち下がりのエッジで入力データを反映する。図6に同期式RSフリップフロップの回路図を示す。

同期式RSフリップフロップは、 Sが1のとき、CPのエッジで出力Qを1にセットし、 Rが1のとき、CPのエッジで出力Qを0にリセットする。 同期式フリップフロップはクロック信号によって動作し、通常はクロックの立ち上がりまたは立ち下がりエッジで入力を受け付ける。表1に真理値表を、図6(右)にタイミングチャートを示す。表1にあるように、出力Qの不定な状態は、SとRが同時に1の場合に発生する。これを避けるために、通常は正確なタイミングでSとRを同時に1にしないようにする。

| \(CP\) | \(S\) | \(R\) | \(Q\) | \(\overline{Q}\) |

| \(0 \rightarrow 1\) | 0 | 0 | 前の\(Q\) | 前の\(\overline{Q}\) |

| \(0 \rightarrow 1\) | 1 | 0 | 1 | 0 |

| \(0 \rightarrow 1\) | 0 | 1 | 0 | 1 |

| \(0 \rightarrow 1\) | 1 | 1 | 不定 | 不定 |

Dフリップフロップ

Dラッチ

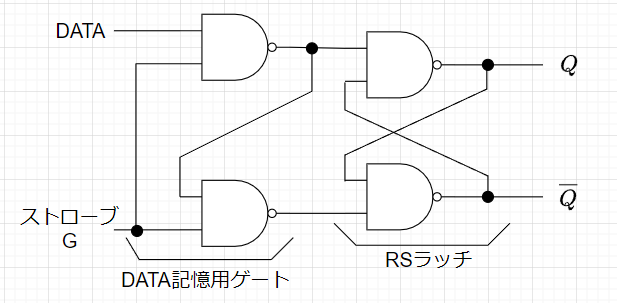

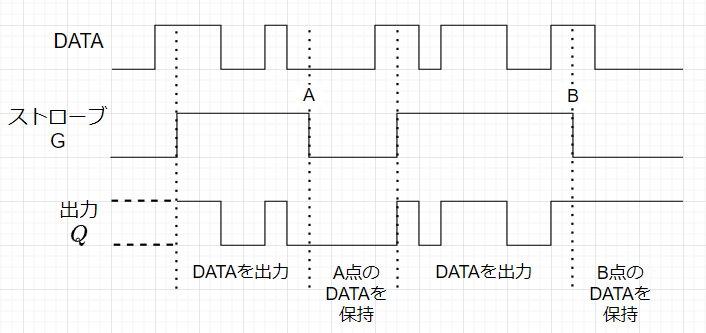

Dラッチは、1ビットのデータを格納するのに用いられる。Dラッチは、入力端子DATA、ストローブG、出力端子\(Q\)、そして補助的な出力端子\(\overline{Q}\)を持つ。Dラッチは、ストローブGの立ち上がりエッジに応じて入力データを出力に反映する同期式の素子である。Dラッチの基本的な動作は、ストローブGの立ち上がりエッジ(0から1の変化)、または、立ち下がり(1から0の変化)のエッジで、DATAの値がラッチに格納される。ストローブGの立ち上がりエッジで、DATAの値が\(Q\)にコピーされ、ストローブGの立ち下がりエッジでは、DATAの値が変化してもQは更新されず、前の値を保持する。

図7にDラッチの論理回路図、図8に動作のタイミングチャート、図9に真理値表を示す。

| ストローブG | \(DATA\) | \(Q\) | \(\overline{Q}\) |

| \(0 \rightarrow 1\) | 0 | 0 | 1 |

| \(0 \rightarrow 1\) | 1 | 1 | 0 |

| \(1 \rightarrow 0\) | ー | 前の\(Q\)を 保持 | 前の\(\overline{Q}\)を 保持 |

Dフリップフロップ

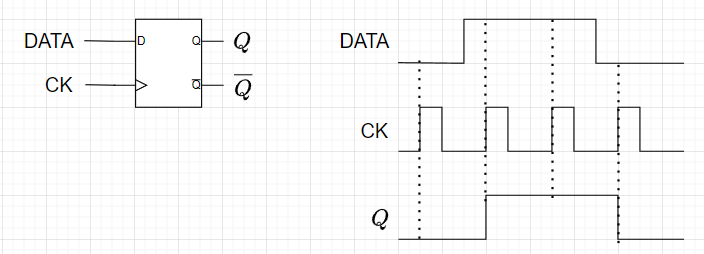

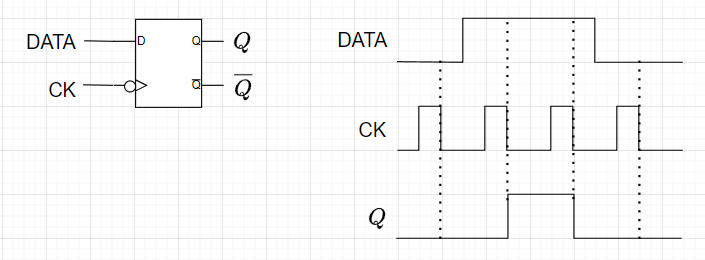

Dフリップフロップは、1つのデータ入力DATA(D)、1つのクロック入力(CK)、および2つの出力(\(Q, \; \overline{Q}\))をがある。Dフリップフロップは、CKの立ち上がりまたは立ち下がりのエッジで入力データを出力に反映するようになっている。図9にCKの立ち上がりエッジで動作するタイプのDフリップフロップの回路図とその動作のタイミングチャートを示す。また、図10にCKの立ち下がりエッジで動作するタイプのDフリップフロップの回路図とその動作のタイミングチャートを示す。タイミングチャートより分かるように、Dフリップフロップの基本的な動作では、CKの立ち上がりまたは立ち下がりのエッジで、DATAの値をフリップフロップにコピーし、CKが変化するまでDATAの値を保持する。Dフリップフロップは、CKの立ち上がりまたは立ち下がりのエッジでのみ動作するため、同期式フリップフロップとして知られており、この同期動作により、信号の同時性を保ちつつデータの更新を可能にする。

(立ち上がりエッジ)

(立ち下りエッジ)

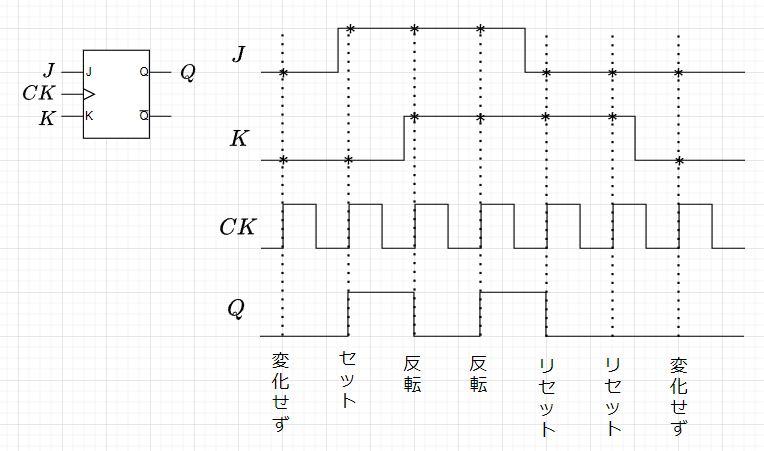

JKフリップフロップ

JKフリップフロップは、2つの入力端子(JとK)、1つのクロック端子(Clock)、および2つの出力端子(\(Q , \; \overline{Q}\))がり、JとKの組み合わせによって異なる動作モードを持ち、通常は同期式の動作をする。J入力とK入力に対して、出力\(Q\)は以下の動作をする。

1)\(J=L\)、\(K=L\)の場合:出力\(Q, \; \overline{Q}\)、\(CK\)が入っても前の状態を保持し、変化しない。

2)\(J=H\)、\(K=L\)の場合:\(CK\)が入ると、出力は、\(Q=H\)、\(\overline{Q}=L\)になる。(セット動作)

3)\(J=L\)、\(K=H\)の場合:\(CK\)が入ると、出力は、\(Q=L\)、\(\overline{Q}=H\)になる。(リセット動作)

4)\(J=H\)、\(K=H\)の場合:\(CK\)が入ると出力が反転する。

図11にJKフリップフロップの回路図記号と動作タイミングチャートを表3に真理値表を示す。

動作タイミングチャート

| \(J\) | \(K\) | 出力 |

| L | L | 変化せず |

| L | H | L(リセット) |

| H | L | H(セット) |

| H | H | 出力反転 |

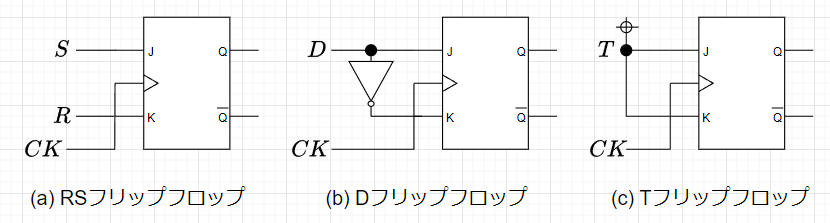

JKフリップフロップの各種フリップフロップへの変換

JKフリップフロップは、RSフリップフロップを基本にしているので、図12(a)のように、J入力をS、K入力をRに対応させれば、同期式RSフリップフロップとして動作する。

図12(b)のようにNOT素子を通して、JとKが互いに反転するように入力した場合、Dフリップフロップと同じ動作をする。

図12(c)のようにJ、KともにHにしておくとCKが加わるたびに出力が反転するTフリップフロップとなる。

このように、JKフリップフロップは、RSフリップフロップ、Dフリップフロップ、Tフリップの機能を兼ね備えており、広く使われている。

“15. フリップフロップ” に対して1件のコメントがあります。

コメントは受け付けていません。