22. 電界効果トランジスタ(FET)

電界効果トランジスタ(Field Effect Transistor:FET)は、半導体の内部に生じた電界によって電流を制御する方式の素子(電圧制御型電流素子)である。FETは、ゲート電極に電圧を加えることで、チャネル領域に生じる電界によって電子または正孔の密度を制御し、ソース・ドレイン電極間の電流を制御する。

FETには、接合型電界効果トランジスタ(JFET)と金属酸化膜半導体電界効果トランジスタ(MOSFET)の2つの種類がある。

JFETは、半導体にp-n接合を形成して作る。p型半導体とn型半導体の接合部に電界(空乏層)が発生し、この電界によってチャネル領域の電荷の密度を制御する。

MOSFETは、半導体の上に金属膜と絶縁膜を形成して作る。ゲート電極の電圧によって、絶縁膜の下にある半導体の表面に電界が発生し、この電界によって反転層を形成し、チャネル領域の電荷の密度を制御する。

FETは、バイポーラトランジスタに比べて、入力インピーダンスが高く、電源電圧が低くできる、などの利点があり、集積回路(IC)で広く用いられている。

JFETの動作原理

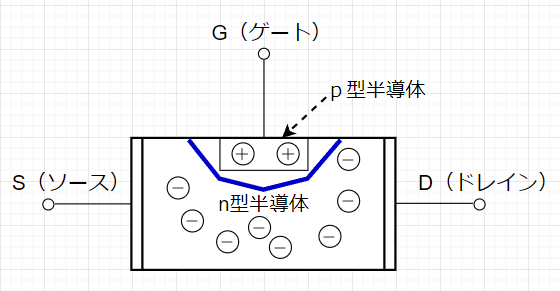

JFET(Junction Field Effect Transistor)・接合型電界効果トランジスタは、電圧制御型電流素子の半導体デバイスで、図1のようにn型(多数キャリアが電子)、またはp型(多数キャリアが正孔)の半導体基板に、逆の型(基板がn型の場合は、p型)の半導体を埋め込みPN接合を形成した構造となっている。このPN接合部分をゲートと呼ぶ。S(ソース)、D(ドレイン)間が電流の通路(チャネル)となる。JFETにはnチャネル型(チャネルをn型半導体としている)とPチャネル型(チャネルをp型半導体としている)の2つの基本タイプがある。

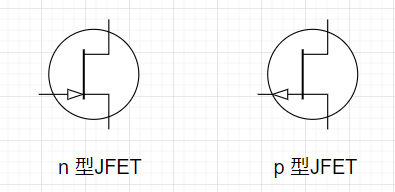

図2がn型JFETとp型JFETの回路図記号例である。これ以外の書き方をした記号もあるが、ゲートの矢印の方向で、p型、n型が区別できる。

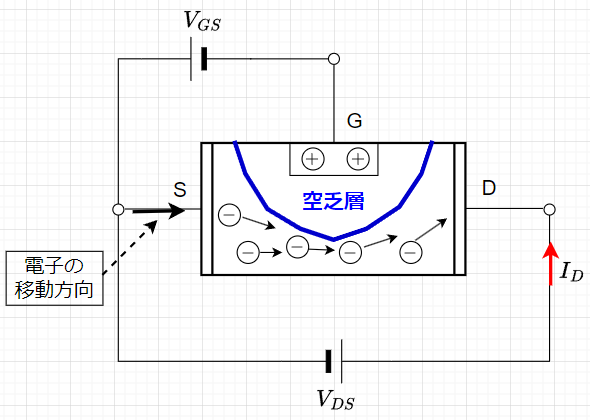

図3はJFETの動作原理図である。JFETはゲートとチャネルと呼ばれる2つの領域を持っており、ゲートにかかる電圧によってチャネルの電流が制御される。ゲートにかかる電圧が変化すると、ゲートとチャネル間の空乏層の幅が変わり、この空乏層がチャネルを狭めることで、チャネル内の電流を制御する。図3のようにゲートとソース間のPN接合に対して、\(V_{GS}\)は逆バイアスとなっているので、\(V_{GS}\)が高くなると空乏層が広がることになる。

MOSFETの動作原理

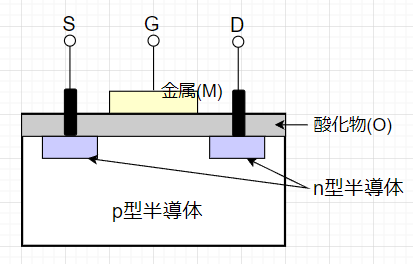

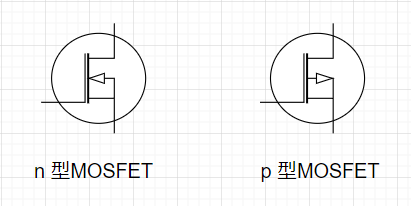

MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)・金属酸化膜半導体電界効果トランジスタは、図4のようにp型(多数キャリアが正孔)、またはn型(多数キャリアが電子)の半導体基板に、逆の型の半導体を対向して埋め込み、それぞれにPN接合を形成し、さらに、酸化物による絶縁層でゲート電極を絶縁した構造になっている。JFETと同様にゲート電圧でドレイン・ソース間の電流を制御する電圧制御型電流素子であるが、JFETと動作原理は異なる。図5はMOSFETの回路図記号である。

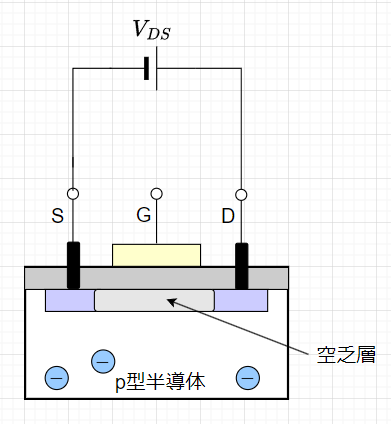

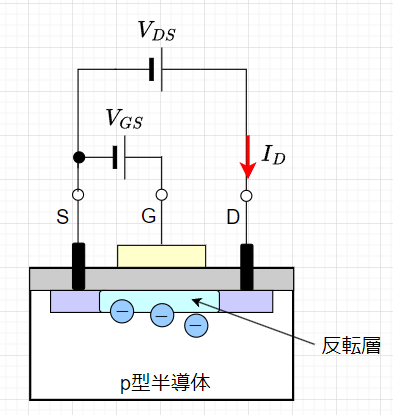

図6,7は、MOSFETの動作原理図である。図6のようにソース・ドレイン間に電圧\(V_{DS}\)をかけると、ドレインとp型半導体基板の間のPN接合部分は、逆バイアスとなり、空乏層が広がり、ドレイン・ソース間に電流が流れない。ここで、図7のようにゲート電圧\(V_{GS}\)を掛けると、ゲート下には正の電界が張るので、p型半導体内の少数キャリアである自由電子が誘導されゲート下に集まる。集まった自由電子により、p型半導体のゲート下では電子が多数キャリアとなり、ソース・ドレイン間に電子が移動できるチャネルが形成される。このチャネルを反転層という。ゲート電圧が高くなるほどこの反転層が厚くなり、電子の移動が容易になる。つまり、ゲート電圧が高くなると、ドレイン・ソース間のドレイン電流\(I_D\)が大きくなる。

MOSFETは、高い入力インピーダンスを持ち、低消費電力である。また、ゲートにかかる電圧によって電流が制御されるため、スイッチングが非常に速く、高い周波数で動作できる。

MOSFETは、現代の集積回路やデジタル回路などで広く使用されており、高い集積度と低消費電力が特長である。

“22. 電界効果トランジスタ(FET)” に対して1件のコメントがあります。

コメントは受け付けていません。