27-1. コルピッツ形発振回路

LTspiceでLC発振回路(コルピッツ形発振回路)をシミュレーションする例を示す。

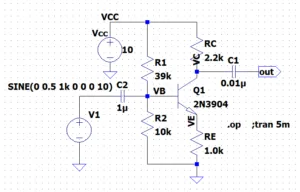

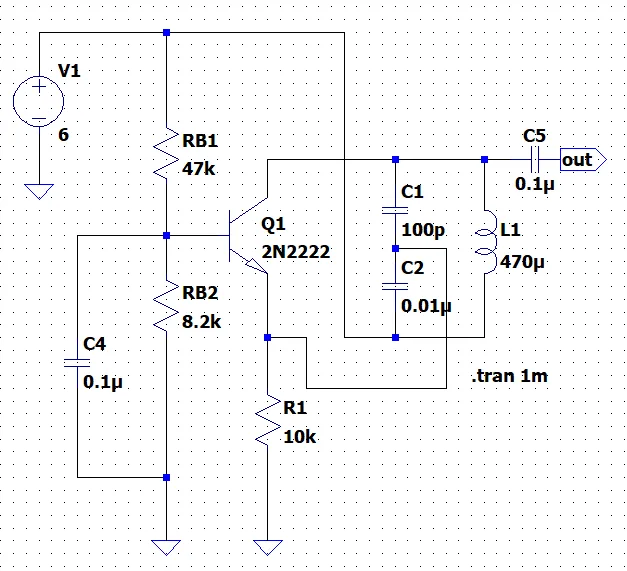

図1に回路例を示す。この回路は、インダクタンス\(L_1\)と、二つのコンデンサ\(C_1, \;C_2\)からなる共振回路(タンク回路)を特徴とする。発振原理については、27. LC発振回路を参照。

回路図の構成要素は、以下となる。

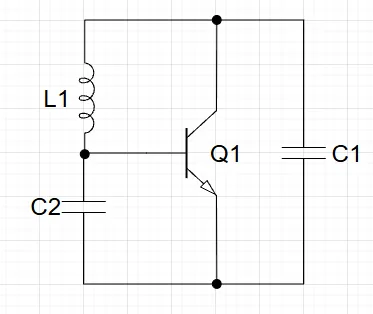

※交流回路を図2に示す。

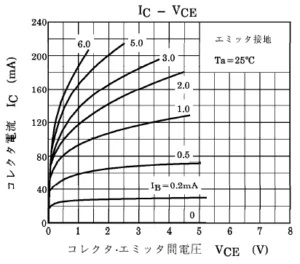

1)増幅部:トランジスタ Q1には、 小信号トランジスタの(2N2222) を使用し、ベースを分圧抵抗RB1とRB2でバイアスする。

2)共振回路(タンク回路): L1、C1、C2 をコレクタとエミッタの間、および電源とGNDの間に接続し、Q1のベースに接続する。図2参照。

3)帰還: C1とC2の共通接続点であるエミッタからベースに信号を帰還させる。(20. 電流帰還直列注入形負帰還増幅回路を参照)

コルピッツ発振回路の発振周波数\(f\)は、共振回路の合成容量 \(C_{\text{eq}}\) とインダクタンス\(L1\)から求められる。$$\frac{1}{C_{\text{eq}}} = \frac{1}{C1} + \frac{1}{C2} \Rightarrow C_{\text{eq}} = \frac{C1\cdot C2}{C1 + C2}\\ f = \frac{1}{2\pi \sqrt{L1 \cdot C_{\text{eq}}}} \quad \text{[Hz]}$$

(LTspice)

図1の回路図の場合、\(L1 = 470\mu\text{H}, C1 = 100\text{pF}, C2 = 0.01\mu\text{F}\)を用いると、$$C_{\text{eq}} = \frac{100\text{pF} \cdot 0.01\mu\text{F}}{100\text{pF} + 0.01\mu\text{F}} \approx 99\text{ pF} \\ f = \frac{1}{2\pi \sqrt{470\times 10^{-6} \cdot 99\times 10^{-12}}} \approx 737.8\text{ kHz}$$

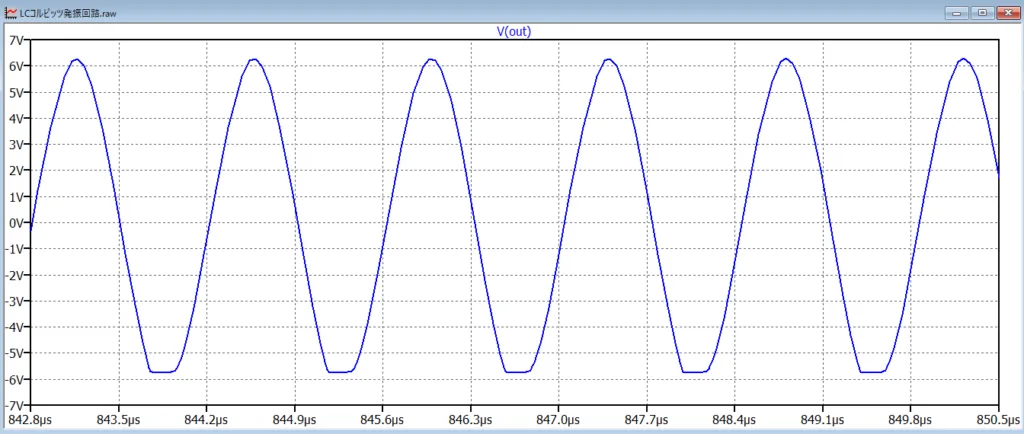

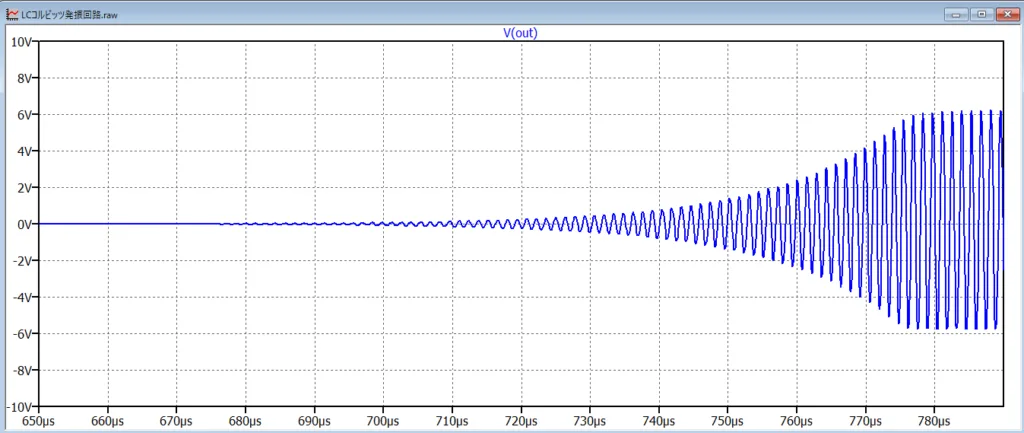

図3は過渡解析シミュレーション結果の発振波形出力(ラベルoutの部分)である。図4は発振の立ち上がり部分を拡大した図である。安定に発振している部分を拡大した図5から発振周波数を読み取ると約\(720 \text{ kHz}\)となることが分かる。

図5を見ると発振波形に歪がみられる。この場合、以下の対策が考えられる。

1)増幅部の線形化:バイアス点を能動領域の中央に設定し、ループゲインを必要最小限まで下げて、ひずみの発生源(増幅器)自体を線形範囲で動作させることを試みる。

2)既存フィルタの強化:共振回路のQ値を向上させることで、ひずみを低減させる。

3)専用フィルタの追加:上記の対策でも要求されるひずみレベルに達しない場合に、外部にBPFなどのフィルタを追加する。